KAIST

BREAKTHROUGHS

Research Webzine of the KAIST College of Engineering since 2014

Spring 2025 Vol. 24

새로운 광학 기술로 기존에는 달성하기 어려웠던 펨토초 (1000조분의 1초) 수준의 정밀한 타이밍과 낮은 발열로 반도체 칩 내에서의 클럭 신호를 생성하고 분배할 수 있게 되었다.

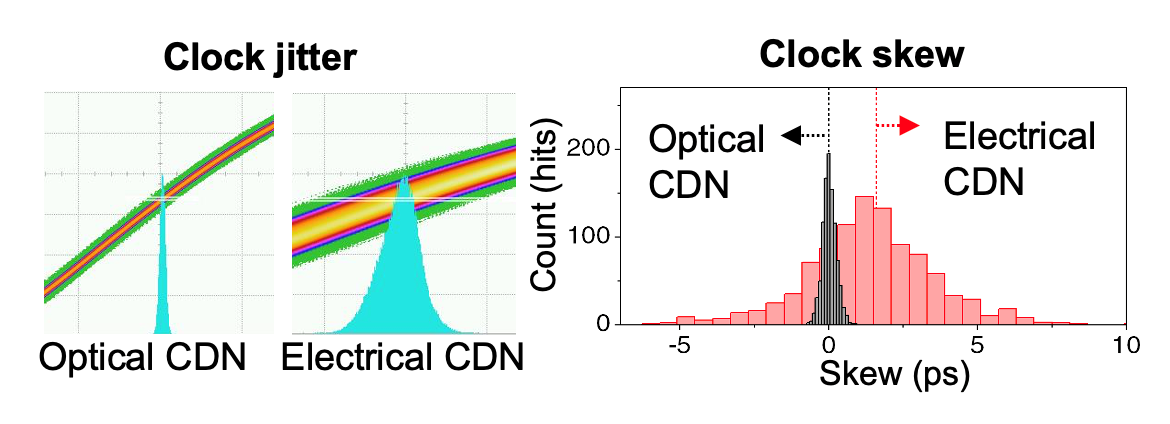

최근 반도체 칩 성능의 급격한 발전과 더불어, 칩 내에서의 보다 정밀하고 정확한 타이밍이 요구되고 있다. 기존의 클럭 분배 네트워크(CDN)의 경우 많은 수의 클럭 드라이버들을 사용함으로 인해 타이밍 성능이 제한되었으며 칩 내 열 발생 문제도 있었다. 그 결과 지터 (랜덤한 타이밍의 변화) 및 스큐 (공간적인 타이밍의 변화)가 모두 수에서 수십 피코초 정도로 제한되었다.

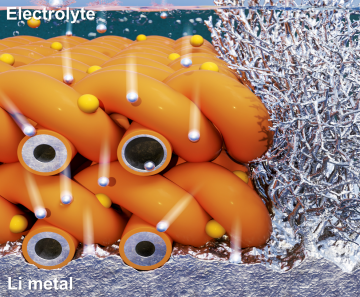

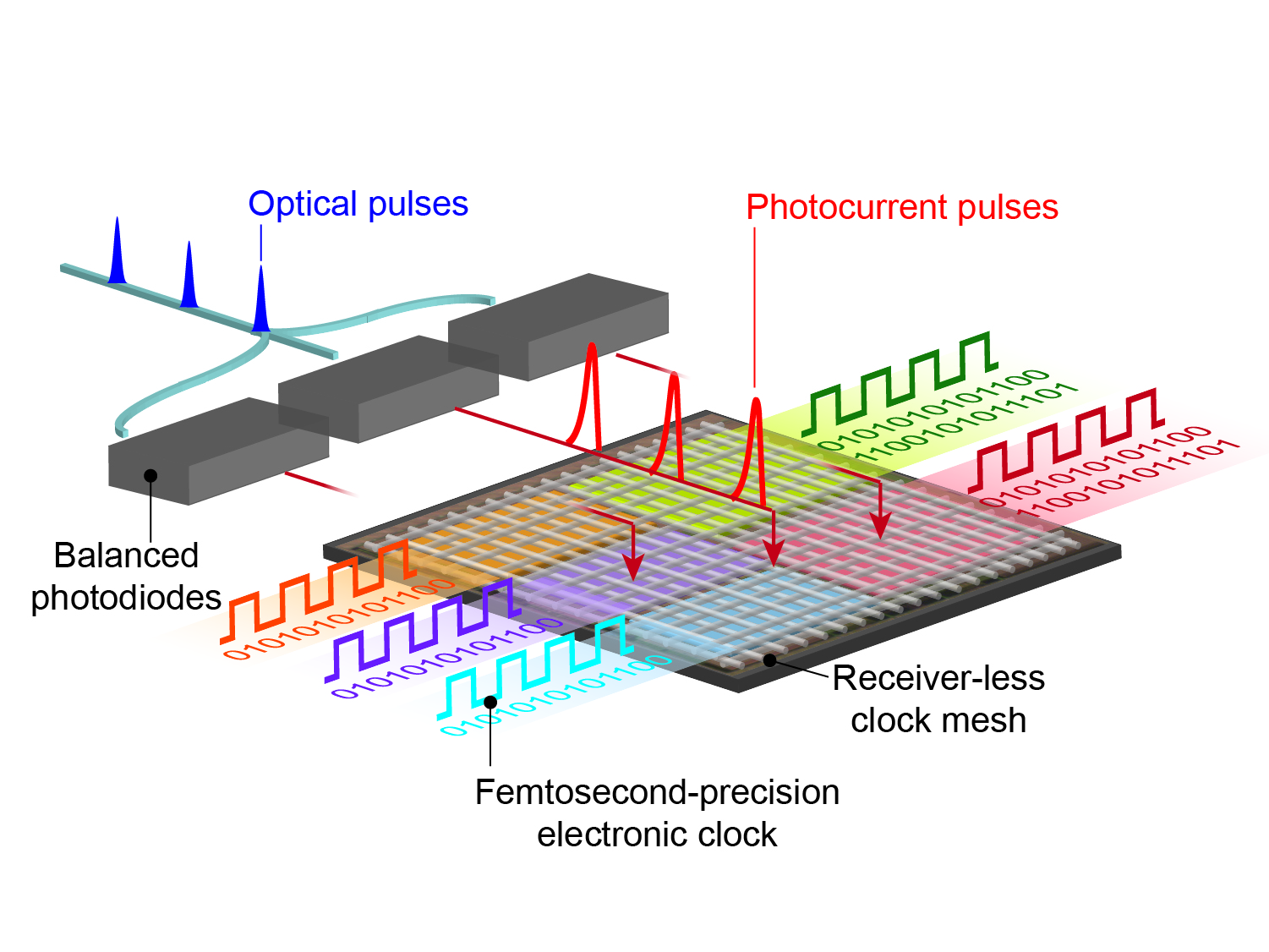

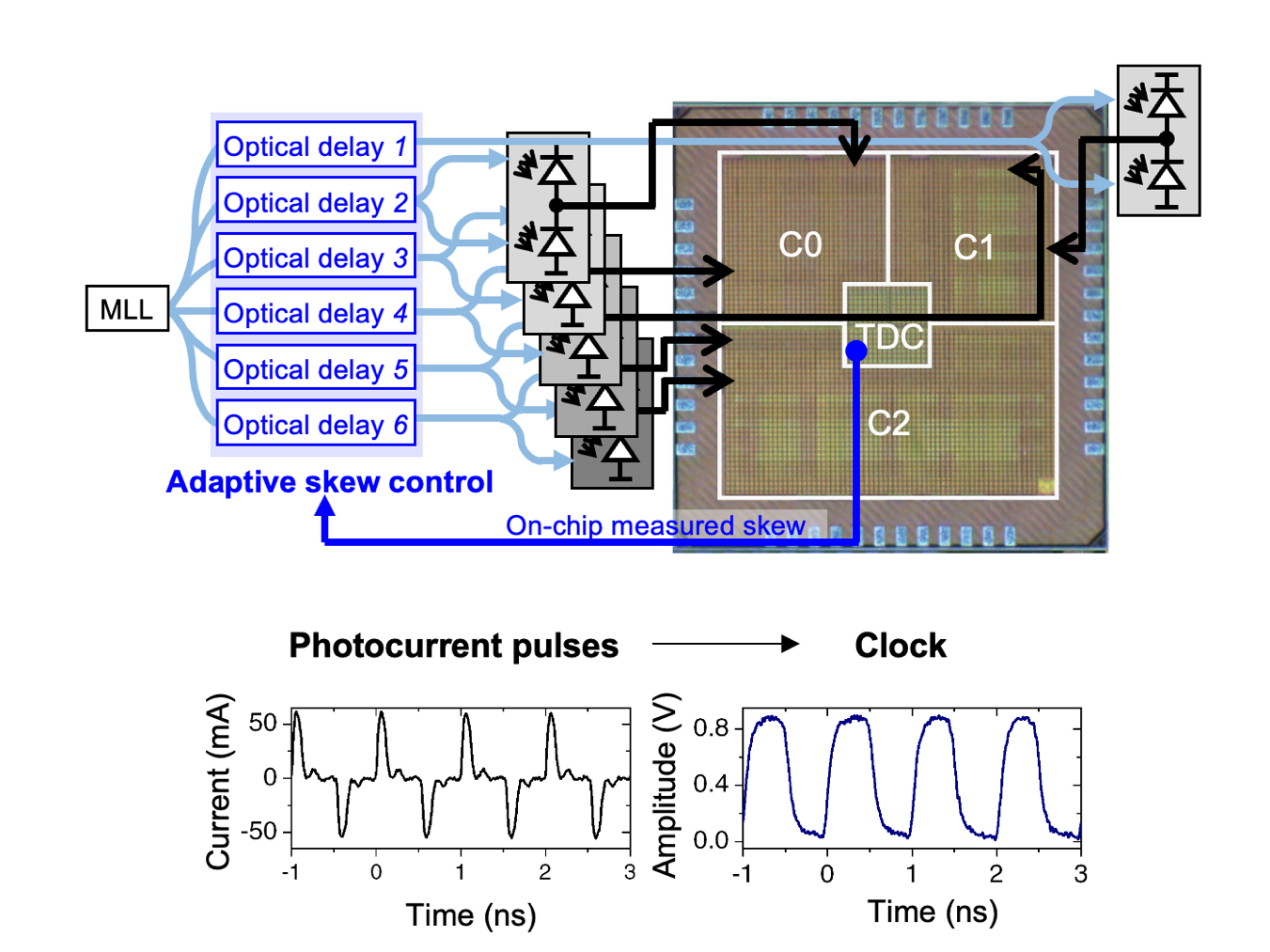

KAIST 김정원 교수가 이끄는 KAIST-고려대 공동 연구팀은 펨토초 이하의 타이밍 지터를 가지는 광주파수빗 광원을 마스터 클럭으로 사용한 새로운 광학적인 방법을 이용하여 이 문제를 해결할 수 있었다. 광주파수빗으로부터 생성되는 빛 펄스들은 고속 광다이오드를 이용해서 광전류 펄스로 변환된 후 칩 내의 금속 구조를 충전/방전함으로써 사각파 형태의 클럭 신호를 생성할 수 있었다.

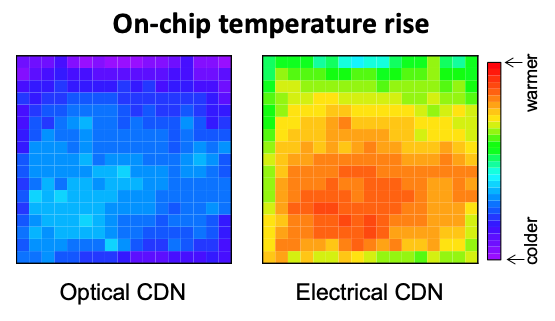

이 방법은 특히 칩 내에서 클럭 드라이버 없이 금속 구조만을 사용하여 클럭을 분배할 수 있어 타이밍 성능을 획기적으로 향상시킬 수 있었을 뿐 아니라 칩내 열 발생도 줄일 수 있었다. 그 결과 지터와 스큐를 모두 20펨토초 이하로 만들 수 있었으며 이는 기존 방식들과 비교하여 100배 이상 향상된 성능이다. 또한 칩 내 클럭 분배에서의 전력 소모와 열 발생도 기존 방식보다 100배 이상 줄일 수 있었다.

김 교수는 “현재 아날로그-디지털 변환기와 같은 고속 회로에서의 샘플링 클럭 지터를 매우 줄인 연구를 수행하고 있다” 고 밝혔으며 “또한 3차원 적층칩과 같은 구조에서의 열 발생을 줄일 수 있는 연구도 계획하고 있다”고 밝혔다.

박사과정 현민지 학생과 고려대 세종캠퍼스 정하연 교수팀과의 공동 연구로 이루어진 연구 결과는 “Femtosecond-precision electronic clock distribution in CMOS chips by frequency comb-extracted photocurrent pulse injection” 라는 제목으로 Nature Communications 지에 게재되었다. 또한 Nature Electronics지 2023년 5월호에 “Chips with a pulse”라는 제목으로 Research Highlights로도 선정되었다.