KAIST

BREAKTHROUGHS

Research Webzine of the KAIST College of Engineering since 2014

Spring 2025 Vol. 24Novel data management in 3D-stacked IC simultaneously reduces thermal density and memory traffic congest

Novel data management in 3D-stacked IC simultaneously reduces thermal density and memory traffic congestion

Prof. Chong-Min Kyung’s research group (http://ssal.kaist.ac.kr) has developed a novel system management algorithm to find an optimal memory data allocation by combining mathematical models of thermal distribution and memory traffic congestion for 3D-stacked IC.

Article | Fall 2014

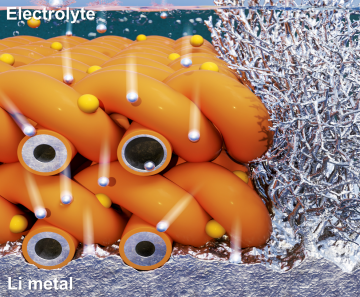

3D memory stacking has received a great deal of attention, as it resolves the memory bandwidth challenges of conventional 2D integrated circuit (IC) systems by stacking cache memory onto a multi-core die (see an illustrated target 3D-stacked memory system in the figure below). However, the high power density resulting from multiple memory die stacking may lead to temperature-related problems in reliability, power, performance, and cooling cost.

There have been several efforts to reduce power consumption by selectively de-activating memory resources at higher operating temperature, but this is expected to lead to unintelligent memory resource allocation due to not considering the processor-memory traffic congestion in 3D-stacked memory systems.

Therefore, Prof. Chong-Min Kyung’s research group proposed an integrated system energy model combined with estimation tools for 3D-structured temperature distribution and memory traffic congestion. 3D temperature distribution is estimated by a coarse-grained thermal model that uses thermal resistance, heat capacitance, and heat current source. Memory traffic in a 3D multi-core system was estimated by a mathematical queuing model using Poisson distribution in memory access rates. The proposed system energy model was applied to an OS task scheduler at runtime since workload characteristics such as memory access and temperature behavior change dramatically at runtime. Prof. Kyung’s group proved that considering both temperature distribution and memory traffic congestion yields a larger system energy reduction (about 23%) than considering only one without the other. The proposed OS task scheduler allocates cache data to the specific physical cache bank position by exploiting the trade-off between the energy induced by memory traffic congestion and the energy induced by the temperature of cache blocks.

This research article was published as the best paper in the 15th IEEE International Symposium on Quality Electronic Design, 2014, and this research is expected to be applied to low energy 3D-stacked CPU systems in the near future.

Most Popular

When and why do graph neural networks become powerful?

Read more

Smart Warnings: LLM-enabled personalized driver assistance

Read more

Extending the lifespan of next-generation lithium metal batteries with water

Read more

Professor Ki-Uk Kyung’s research team develops soft shape-morphing actuator capable of rapid 3D transformations

Read more

Oxynizer: Non-electric oxygen generator for developing countries

Read more